# Measuring Moore's Law: Evidence from Price, Cost, and Quality Indexes

**November 2017 Version**

Kenneth Flamm

Kenneth Flamm University of Texas at Austin kflamm@mail.utexas.edu

Preliminary Early Draft

#### **Measuring Moore's Law**

#### Kenneth Flamm

#### November 2017

"Moore's Law" in the semiconductor manufacturing industry is used to describe the predictable historical evolution of a single manufacturing technology platform ("silicon CMOS") that has been continuously reducing the costs of fabricating electronic circuits since the mid-1960s. Some features of its future evolution were first correctly predicted by Gordon E. Moore (then at Fairchild Semiconductor) in 1965, and Moore's Law became an industry synonym for continuous, periodic reduction in both size and cost for electronic circuit elements.

Technological innovation for this manufacturing platform was coordinated and synchronized across a variety of different engineering fields, including materials, optical systems, ultraclean precision manufacturing, factory automation, electronic circuit design and simulation, and improved computer software for computational modelling in all of these fields. It was a self-reinforcing dynamical process, since the largest market for the semiconductor manufacturing industry's products has always been the computer industry.¹ Cheaper computing hardware meant cheaper modeling and engineering to further reduce the costs of the semiconductors manufactured for use in future computers. New public-private institutions and organizations were developed to coordinate the simultaneous arrival of the very heterogeneous technological building blocks required for this increasingly complex semiconductor manufacturing technology platform.

The result was an industrial dynamic that, since the mid-1960s, had effectively worked as a "virtual shrinking machine" for electronic circuits. On a regular basis, new "technology nodes" delivered 30 percent reductions in the size of the smallest dimension ("critical feature size," F) that could be reliably manufactured on a silicon wafer. This implied a 50 percent reduction in the area occupied by the smallest manufacturable electronic circuit feature (F²), and a doubling in density—the number of circuit elements (e.g., transistors) per area of silicon in a chip. Section 1 develops some stylized economic facts, reviewing why this progression in manufacturing technology delivered a 20 to 30 percent annual decline in the cost of manufacturing a transistor, on average, as long as it continued.

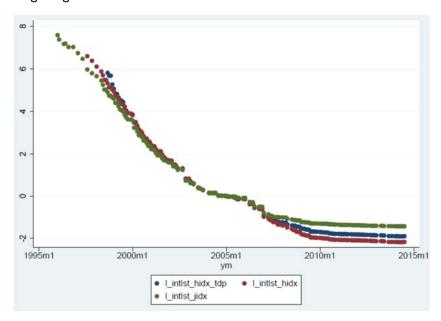

Section 2 reviews other economically significant benefits (in addition to increased density and lower cost per circuit element) that would be associated with smaller feature sizes. Some of those characteristics would be expected to have significant economic value, and historical trends for these characteristics are reviewed. Chip speed, in particular, would have major impacts on computer performance. Econometric analysis of software benchmark data shows rates of performance improvement in CPUs declining dramatically in the new millennium, a retreat from very high rates of increase measured in the late 1990s. Lower manufacturing costs alone pose no special challenges for price and innovation measurement, but these other benefits do, and motivate quality adjustment methods when semiconductor product prices are measured.

<sup>&</sup>lt;sup>1</sup> Defining the computer industry expansively, to include the computer systems embedded in the smart electronic systems and mobile devices whose sales have grown most rapidly in recent decades.

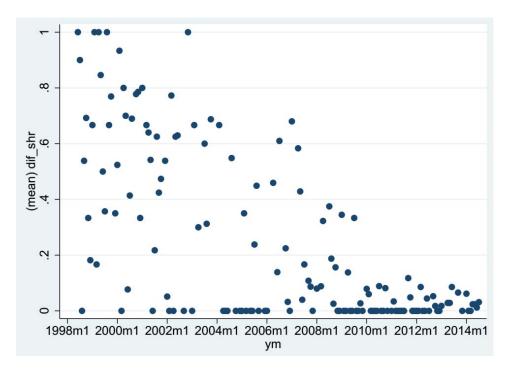

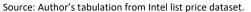

Section 3 analyzes empirical evidence of recent changes to the historical Moore's Law trajectory, and finds corroborating evidence for a slowdown in Moore's Law in prices for the highest volume products: memory chips, custom chip designs outsourced to dedicated contract manufacturers (foundries), and Intel microprocessors. Section 4 reviews evidence to the contrary, which paradoxically, also relates primarily to Intel microprocessors, and discusses economic reasons why Intel microprocessor prices might behave differently from prices for other types of semiconductor chips.

Section 5 dives into microprocessors in greater depth, and tests the computer architecture textbook view of how a small set of specific chip characteristics affect performance of microprocessors in executing programs, by outlining a structural model of microprocessor computing performance, then estimating that model empirically. This simple econometric model, using only a small set of explanatory chip characteristics, explains 99% of variance across processor models in performance on commonly used CPU performance benchmarks. These characteristics, which determine benchmark scores, should clearly be included in any hedonic price equation. Most of these chip characteristics would also be expected to affect chip production cost, and would therefore have an additional rationale for inclusion in a hedonic price equation quite apart from their role in determining computer performance benchmark scores.

# 1. Stylized Facts About Semiconductor Manufacturing Innovation

In 1965, five years after the integrated circuit's invention, Gordon E. Moore (who would shortly move on to co-found Intel) predicted that the number of transistors (circuit elements) on a single chip would double every year. Later modifications of that early prediction—"Moore's Law"—became shorthand for semiconductor manufacturing innovation.

Moore's prediction requires other assumptions in order to create economically meaningful connections to the information age's key economic variable: the cost (or price) of electronic functionality on a chip (embodied in the 20<sup>th</sup> century's supreme electronic invention, the transistor).<sup>3</sup> Chip fabrication requires coordinating multiple technologies, combined in very complex manufacturing processes.

The pacing technology has been the photolithographic processes used to pattern chips. From the 1970s through the mid-1990s, a new "technology node" — a new generation of photolithographic and related equipment, and materials required for successful use—was introduced roughly every three years or so. Starting in the mid-1970s, three years also happened to be the time interval between introductions of next-generation DRAM computer memory chips, storing four times the bits in the previous generation chip.<sup>4</sup> This observed 18-month "doubling period" became a new, *de facto*, "revised" Moore's law.<sup>5</sup>

<sup>&</sup>lt;sup>2</sup> Moore (1965).

<sup>&</sup>lt;sup>3</sup> Jorgenson (2001), Flamm (2003), (2004); Aizcorbe, Flamm, and Khurshid, (2007).

<sup>&</sup>lt;sup>4</sup> The DRAM memory was invented in 1968 by Robert Dennard at IBM, and first commercialized by Moore's newly founded company, Intel, in 1970.

<sup>&</sup>lt;sup>5</sup> A decade later, Moore himself revised his prediction to a doubling every two years. G. E. Moore, "Progress in digital integrated electronics," in *Tech. Dig. IEEE Int. Electron Devices Meeting*, 1975, pp. 11–13.

The close early fit of DRAM product development cycles with leading edge chip manufacturing technology introductions was no coincidence. DRAMs at that time were the highest volume, standardized, commodity chip product manufactured, and a rapidly expanding computer market drove leading edge chip manufacturing technology development. Moore's prediction morphed into an informal, and later, formal technology coordination mechanism (the International Technology Roadmap for Semiconductors, or ITRS) for the entire global semiconductor industry—equipment and material producers, chip makers, and their customers.

Relationships between Moore's Law and fabrication cost<sup>6</sup> trends for integrated circuits can be described by the following identity, giving cost per circuit element (e.g., transistor):

Moore's original "Law" described only the denominator—a prediction that elements per chip would quadruple every two years. Back in 1965, Moore hadn't originally anticipated rapid future advances in technology nodes. Acknowledging that an IC containing 65,000 elements was implied by 1975, Moore wrote: "I believe that such a large circuit can be built on a single wafer. With the dimensional tolerances already being employed...65,000 components need occupy only about one-fourth a square inch." 7

Rewriting this more concisely without relying on Moore's prediction about numbers of elements per chip (therefore eliminating the need for assumptions about chip size):

which depends directly on the defining characteristic of a new technology node, smallest patternable feature size, as reflected in chip area per transistor. This "Moore's Law" variant came into use in the semiconductor industry as a way of analyzing the economic impact of new technology nodes. New technology nodes increased density of transistors fabricated in a given area of silicon in a readily predictable way. Time between new nodes—and a new node's impact on wafer processing costs—jointly determined decline rates in transistor fabrication cost.

Through 1995, new technology nodes were introduced at roughly three year intervals. Each new node reduced the smallest planar dimension ("critical feature size," F), in circuit elements by 30%, implying 50% smaller silicon areas (F²) per circuit element.

<sup>&</sup>lt;sup>6</sup> Analysis of fabrication costs, which account for most chip cost, ignores assembly, packaging, and test.

<sup>&</sup>lt;sup>7</sup> Moore (1965). The largest wafer sizes in use then were comparable in diameter to a modern snack mini-pizza appetizer.

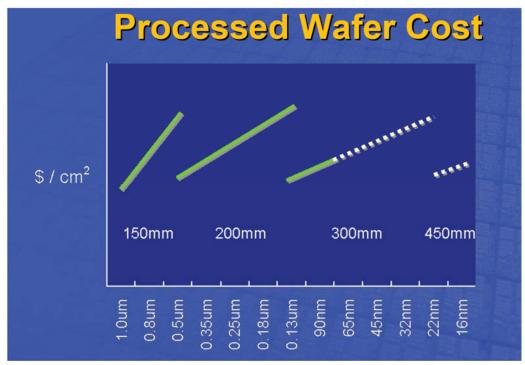

Source: Holt (2005).

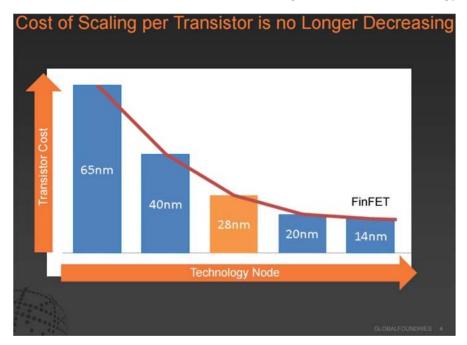

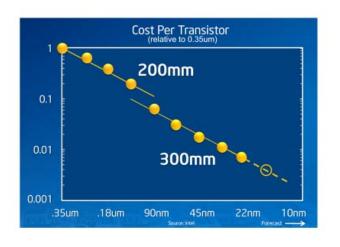

Figure 1. Wafer size conversions offset Intel's increased wafer-processing cost

Completing the economic story, cost per silicon wafer area processed, averaged over long periods, increased only slowly.<sup>8</sup> At new technology nodes, processing cost per silicon wafer area indeed increased. But, episodically, larger wafer sizes were introduced, sharply reducing processing costs per area. The net effect was nearly constant long run costs, with only slight increases. Figure 1, presented in 2005 by Intel's chief manufacturing technologist, shows new wafer sizes "resetting" wafer-processing costs. Significantly, larger diameter wafer sizes (450 mm) were expected at the 22 nanometer (nm) node. However, 450 mm wafers were not introduced as Intel adopted 22 nm technology in 2012, had not been introduced by 2017, and even future introduction now seems highly uncertain. The most recent wafer size "reset," adoption of 300mm diameter wafers, occurred at the 130nm technology node, around 2002.

Using these stylized trends—wafer-processing cost per area of silicon roughly constant, and silicon area per circuit element halved with new technology nodes introduced every three years—equation (2) above predicts that every three years, the cost of producing a transistor would fall by 50%, a 21% compound annual decline rate.

In reality, leading edge computer chips—like DRAM memory (the primary product originally produced at Intel after Moore and others founded that company, which immediately became the largest volume product in the semiconductor industry and the primary product driving Intel's initial growth)—

<sup>&</sup>lt;sup>8</sup> Over 1983-1998, wafer-processing cost/cm<sup>2</sup> silicon increased 5.5 percent annually. Cunningham et. al. (2000), p. 5. This estimate relates to total silicon area processed (including defective chips). Since defect-free chips' share of total processed area increased historically, wafer-processing cost per good silicon area rose even more slowly, approximating constancy.

dropped in price substantially faster than 20% pre-1985. The steeper decline rate in part reflected further increases in density due to circuit design improvements (e.g., reduction in memory cell footprint)<sup>9</sup>, 3-D interconnect layers enabling tighter packing of circuit elements,<sup>10</sup> and gradual introduction of 3-D into physical designs of transistors and other circuit elements.<sup>11</sup> In addition, operating characteristics of a given circuit design—in particular, switching speed and power requirements—improved with new manufacturing technology, and made additional contributions to quality-adjusted price. Finally, smaller and cheaper transistors made it economic to add ever greater electronic functionality to chips, and more and more of a complete electronic system was progressively integrated onto a single chip, which greatly improved system reliability.<sup>12</sup>

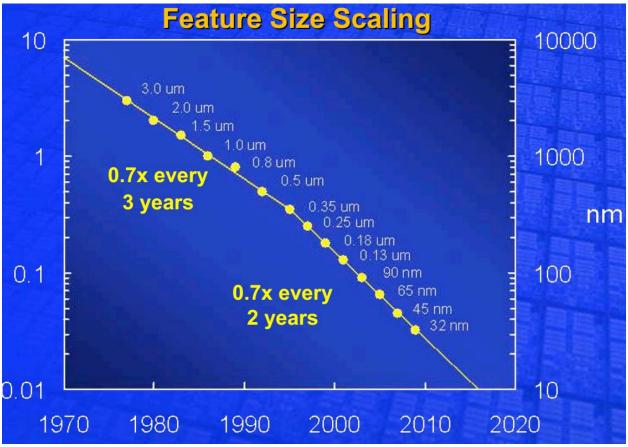

In the mid-1990s, the semiconductor manufacturing industry arrived at a significant technological inflection point.<sup>13</sup> New technology nodes began arriving at two-year intervals, replacing three-year cycles. (Intel's perception of this trend, as of 2005, is documented in Figure 2.) The origins of this change lie in the early 1990s, when the U.S. SEMATECH R&D consortium sponsored a roadmap coordination mechanism in pursuit of an acceleration in the introduction of new manufacturing technology, intended to benefit the competitiveness of US chip producers. By the mid-1990s, with the increasing reliance of semiconductor manufacturing on a global industrial supply chain, the American national roadmap evolved into the international ITRS.<sup>14</sup> Explicitly coordinating the simultaneous development of the many complex technologies required to enable a new manufacturing technology node every two years apparently succeeded in raising the tempo of semiconductor manufacturing innovation for over a decade.<sup>15</sup>

The mid-1990s were also a technological inflection point for Intel's manufacturing capabilities. Intel had exited the DRAM business in 1985, which previously had been driving its leading edge manufacturing technology development, and refocused its R&D on logic circuit design. Burgelman (1994), pp. 32-46. As a consequence, by the late 1980s, Intel manufacturing capability was trailing well behind the leading edge of the manufacturing technology it had once pioneered.

In order to catch up, Intel began adopting new nodes every two years, even as the rest of the industry continued at the historical three year pace. Comparing launch dates for Intel processors at new technology nodes with initial use of those nodes by DRAM makers: Intel was 2 years behind in 1989 (at 1000nm); 3 years behind in 1991 (800nm); 1 year behind in 1995 (350nm). Intel caught up with the DRAM makers in 1997, at 250nm, and remained on a roughly 2 year cycle through 2014. Author's calculations based on Intel (2008), IC Knowledge (2004), <a href="https://ark.intel.com">https://ark.intel.com</a>.

<sup>&</sup>lt;sup>9</sup> Flamm (2010), Figure 2, documents a 62 percent decline in minimum memory bit cell footprint between 1995 and 2004.

<sup>&</sup>lt;sup>10</sup> Anticipated by Moore in 1965: "no space wasted for interconnection…using multilayer metallization patterns separated by dialectric films.." Moore (1965).

<sup>&</sup>lt;sup>11</sup> Recent examples of 3-D transistor structures include RCAT (recessed cell array transistor) and FinFET (fin field effect transistor) structures. 3-D capacitor designs have been used in DRAM since the late 1990s.

<sup>&</sup>lt;sup>12</sup> Since electrical interconnections between components have historically been the most frequent point of failure in electronic systems.

<sup>&</sup>lt;sup>13</sup> Industry roadmaps originally dated this transition to two-year node rollouts to 1995; post-2004 roadmaps revised that date to 1998. Aizcorbe, Oliner, and Sichel, (2006) have persuasively argued that the turning point was closer to mid-1990s than late in the decade.

<sup>&</sup>lt;sup>14</sup> Flamm (2009); Spencer and Seidel (2004).

<sup>&</sup>lt;sup>15</sup> The last (incomplete) official roadmap prepared by ITRS was released in 2012. Intel and others reportedly withdrew from ITRS around this time.

Source: Holt (2005).

Figure 2. Feature Size Scaling as Observed by Intel in 2005

Using (2), but adopting shorter two-year cycles for new technology nodes, implies rates of annual decline in transistor cost accelerating to almost 30%. In short, if the historic pattern of 2-3 year technology node introductions, combined with a long run trend of wafer processing costs increasing very slowly were to have continued indefinitely, a minimum floor of perhaps a 20 to 30 percent annual decline in quality-adjusted costs for manufacturing electronic circuits would be predicted, due solely to these "Moore's Law" fabrication cost reductions. On average, over long periods, the denser, "shrink" version of the same chip design fabricated year earlier would be expected to cost 20 to 30 percent less to manufacture, purely because of the improved manufacturing technology.

It now appears that this two-year cycle for technology nodes definitively ended in 2014, with deployment of the 14nm node. The most aggressive adopter of leading edge chip manufacturing technology, Intel, currently projects introduction of its next 10nm processor products no earlier than late 2018. This means that time between introductions of new technology nodes now is approaching 4 years for Intel, a dramatic change from its two-year cadence through 2014<sup>17</sup>

<sup>&</sup>lt;sup>16</sup> See <a href="http://wccftech.com/intel-delays-10nm-cannon-lake-cpus-end-2018/">http://wccftech.com/intel-delays-10nm-cannon-lake-cpus-end-2018/</a>.

<sup>&</sup>lt;sup>17</sup> Intel chip manufacturing competitor TSMC was said in early 2017 to be manufacturing a "10nm" node in volume for Apple (See R. Merritt, "TSMC, Samsung Diverge at 7nm," *EE Times*, Feb. 8, 2017, (<a href="http://www.eetimes.com/document.asp?doc\_id=1331324">http://www.eetimes.com/document.asp?doc\_id=1331324</a>), but it is widely believed in the industry that its current technology is physically equivalent to a half node advancement over the previous generation Intel

At Intel, the post-1995 two-year technology development cycle had been explicitly incorporated into marketing efforts, and dubbed the Intel "tick-tock" development model in 2007. Every two years, there would be a new technology node introduced ("tick"), with the existing microprocessor computer architecture ported to the new node (effectively "die shrinks" using the new process), followed by an improved architecture fabricated with the same technology the following year ("tock"). The death of the "tick-tock" model was formally acknowledged by Intel in its 2016 annual report. 19

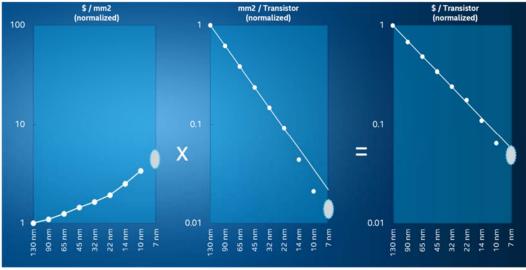

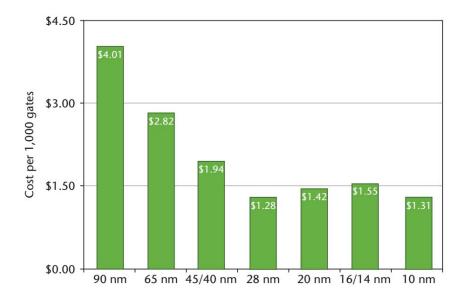

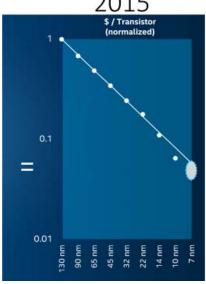

Intel publicly disclosed a version of equation (2) to its shareholders in 2015, purged of sensitive cost numbers by indexing all variables to equal one at the 130nm technology node, the technology node at which the transition to a larger wafer size occurred<sup>20</sup>. The 2015 Intel decomposition of manufacturing cost per transistor, using equation (2), is shown as Figure 3, and in Table 1. Generally, Intel's average silicon area per transistor did not decline by the predicted 50% between technology nodes, primarily because of the increasing complexity of interconnections in processor designs.<sup>21</sup> If accurate, these numbers indicate average chip area per transistor shrank by 38% at each new node from 130nm through 22nm.<sup>22</sup> Nor did Intel's wafer-processing costs stay constant over the post-130nm period as a whole, since the adoption of 450mm wafers, and subsequent cost reset, never happened at 22nm, as had been predicted back in 2005. However, as long as average area per transistor declined at faster rates than processing costs per area increased, transistor cost would continue to decline. Intel's cost per transistor estimates are revisited below.

Source: Holt (2015).

Figure 3. Intel 2015 Version of Equation (2)

technology node. See <a href="https://www.semiwiki.com/forum/f293/intel-tsmc-samsung-10nm-update-8565.html">https://wccftech.com/intel-losing-process-lead-analysis-7nm-2022/</a>.

<sup>&</sup>lt;sup>18</sup> See http://www.intel.com/pressroom/archive/releases/2007/20070918corp a.htm .

<sup>&</sup>lt;sup>19</sup> Intel (2016), p. 14.

<sup>&</sup>lt;sup>20</sup> Intel actually produced microprocessors in volume on both 200mm (8") and 300mm (12") wafers using its 130nm manufacturing process technology. See Natrajan, at. al., (2002), pp. 16-17.

<sup>&</sup>lt;sup>21</sup> See Flamm (2017), p. 34, for a more detailed explanation.

<sup>&</sup>lt;sup>22</sup> Absolute constancy in reported decline rates for average area per transistor over five generations of new Intel manufacturing technology is puzzling, suggesting long-run trend-based estimates rather than actual averages computed from empirical manufacturing data.

|         | Wafer<br>Processin                      |                                                       |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                         |                                                                                                                                                             |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                |

|---------|-----------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | g Cost (\$ /<br>mm²)                    |                                                       | Transistor size (mm² / transistor)                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | \$ Cost /<br>Transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                         | Wafer<br>Processing<br>Cost (\$ /<br>mm <sup>2</sup> )                                                                                                      | Transistor size (mm² / transistor)                                                                                                                                                                               | \$ Cost /<br>Transistor                                                                                                                                                                                                                                                                                                                        |

|         |                                         |                                                       |                                                                                  | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                         |                                                                                                                                                             |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                |

| 130     | 1                                       |                                                       | 1                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                                                                                             |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                |

| 90      | 1.09                                    |                                                       | 0.62                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                         | 5%                                                                                                                                                          | -21%                                                                                                                                                                                                             | -18%                                                                                                                                                                                                                                                                                                                                           |

| 65      | 1.24                                    |                                                       | 0.38                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                         | 7%                                                                                                                                                          | -21%                                                                                                                                                                                                             | -16%                                                                                                                                                                                                                                                                                                                                           |

| 45      | 1.43                                    |                                                       | 0.24                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                         | 7%                                                                                                                                                          | -21%                                                                                                                                                                                                             | -15%                                                                                                                                                                                                                                                                                                                                           |

| 32      | 1.64                                    |                                                       | 0.15                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                         | 7%                                                                                                                                                          | -21%                                                                                                                                                                                                             | -16%                                                                                                                                                                                                                                                                                                                                           |

| 22      | 1.93                                    |                                                       | 0.09                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                         | 8%                                                                                                                                                          | -21%                                                                                                                                                                                                             | -14%                                                                                                                                                                                                                                                                                                                                           |

| 14      | 2.49                                    |                                                       | 0.04                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                         | 14%                                                                                                                                                         | -31%                                                                                                                                                                                                             | -22%                                                                                                                                                                                                                                                                                                                                           |